the small systems journal

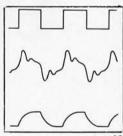

Cassette Interfaces

Microprocessor Update: CPI600

More on Algebraic Expressions

Hand Assembly

Space Ace

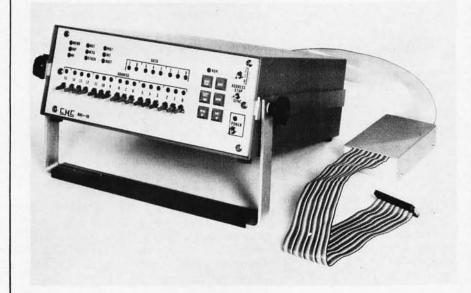

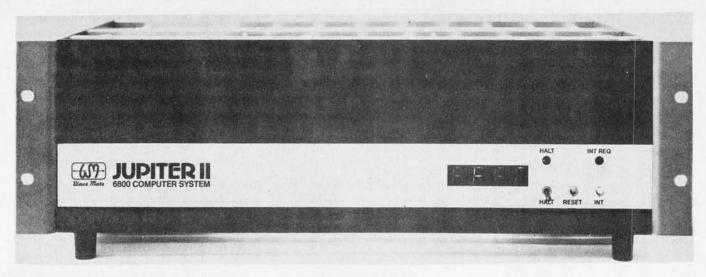

## WHY SETTLE FOR LESS— THAN A COMPLETE 6800 SYSTEM

#### MEMORY-

All static memory with selected 2102 IC's allows processor to run at its maximum speed at all times. No refresh system is needed and no time is lost in memory refresh cycles. Each board holds 4,096 words of this proven reliable and trouble free memory. Cost—only \$125.00 for each full 4K memory.

#### INTERFACE—

Serial control interface connects to any RS-232, or 20 Ma. TTY control terminal. Connectors provided for expansion of up to eight interfaces.

Unique programmable interface circuits allow you to match the interface to almost any possible combination of polarity and control signal arrangements. Baud rate selection can be made on each individual interface. All this at a sensible cost of only \$35.00 for either serial, or parallel type

#### PROCESSOR—

"Motorola" M6800 processor with Mikbug® ROM operating system. Automatic reset and loading, plus full compatability with Motorola evaluation set software. Crystal controlled oscillator provides the clock signal for the processor and is divided down by the MC14411 to provide the various Baud rate outputs for the interface circuits. Full buffering on all data and address busses insures "glitch" free operation with full expansion of memory and interfaces.

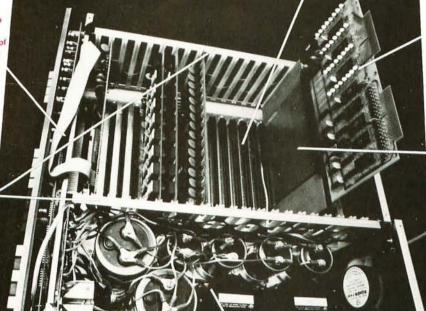

### POWER SUPPLY—

Heavy duty 10.0 Amp power supply capable of powering a fully expanded system of memory and interface boards. Note 25 Amp rectifier bridge and 91,000 mfd computer grade filter capacitor.

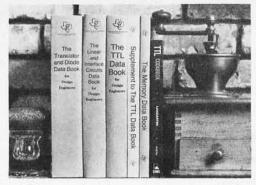

#### DOCUMENTATION-

Probably the most extensive and complete set of data available for any microprocessor system is supplied with our 6800 computer. This includes the Motorola programming manual, our own very complete assembly instructions, plus a notebook full of information that we have compiled on the system hardware and programming. This includes diagnostic programs, sample programs and even a Tic Tac Toe listing.

Mikbug<sup>®</sup> is a registered trademark of Motorola Inc.

with serial interface and 2,048 words of memory......\$395.00

|   |    |        |          |       | ////////////////////////////////////// |

|---|----|--------|----------|-------|----------------------------------------|

|   |    |        |          |       |                                        |

|   | 4  |        |          |       |                                        |

| 1 | 50 | iii 68 | DO SOMPU | TER I |                                        |

|         | my SwTPC Computer Kit Send Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| or BAC  | #                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| □ or MC | Ex Date                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| NAME    | The second secon |

| ADDRESS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

### In the Queue

#### Foreground

| THE COMPLEAT TAPE CASSETTE INTERFACE10 |

|----------------------------------------|

| Systems-Hemenway                       |

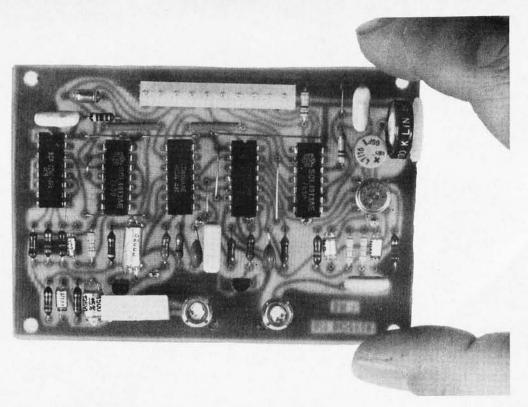

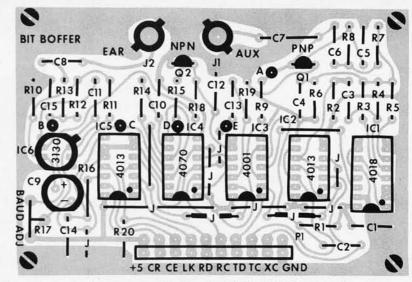

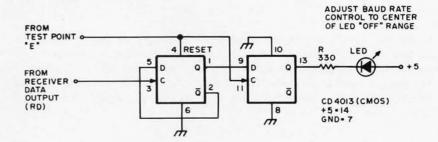

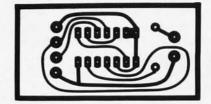

| BUILD THE BIT BOFFER                   |

| Hardware-Lancaster                     |

| DIGITAL DATA ON CASSETTE RECORDERS     |

| Hardware—Mauch                         |

| ASSEMBLING PROGRAMS BY HAND            |

| Software-Helmers                       |

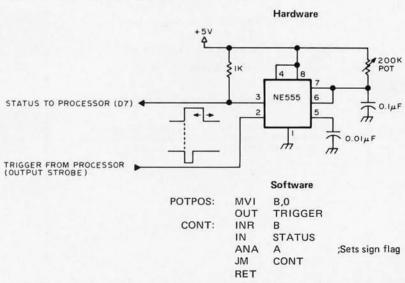

| POT POSITION DIGITIZING IDEA79         |

| Hardware-Schulein                      |

#### Background

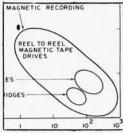

| MAGNETIC RECORDING FOR COMPUTERS           |

|--------------------------------------------|

| Hardware—Manly                             |

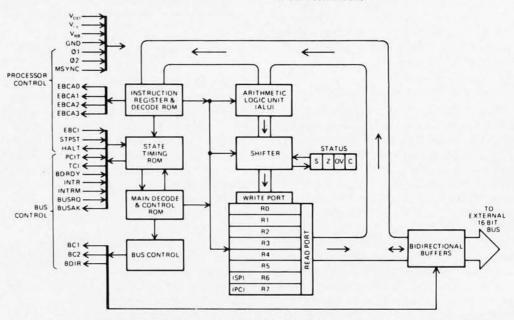

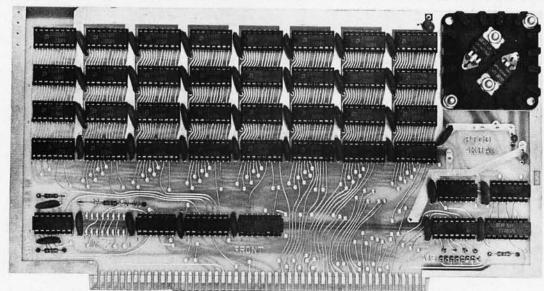

| MICROPROCESSOR UPDATE: CP1600              |

| Hardware-Baker                             |

| PROCESSING ALGEBRAIC EXPRESSIONS, PART 262 |

| Software-Maurer                            |

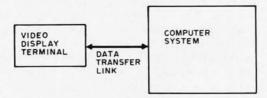

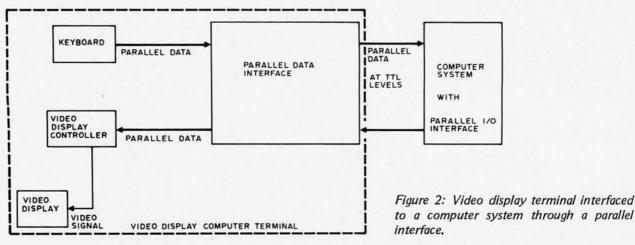

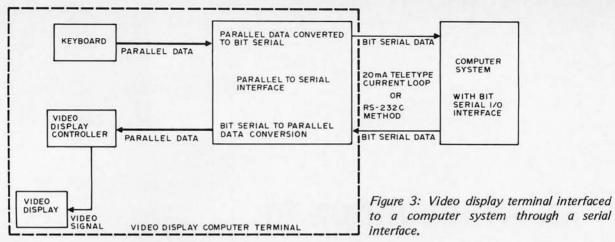

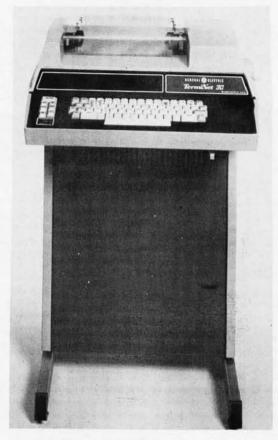

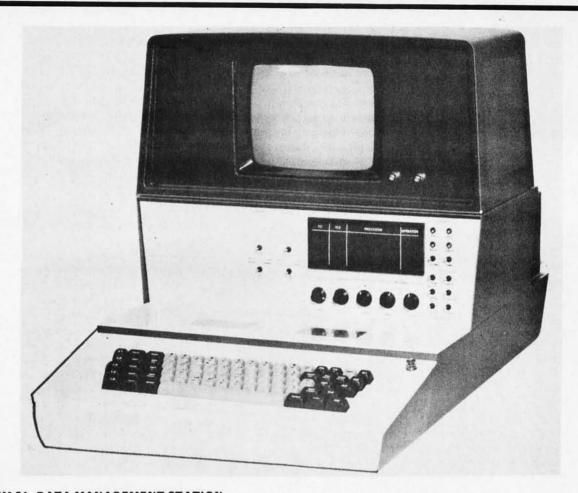

| WHAT'S IN A VIDEO DISPLAY TERMINAL         |

| Systems-Walters                            |

#### Nucleus

| In This BYTE                  | 2 |

|-------------------------------|---|

| Magnetic Recording Technology | 6 |

| Technology Update             | 9 |

| Letters                       | 8 |

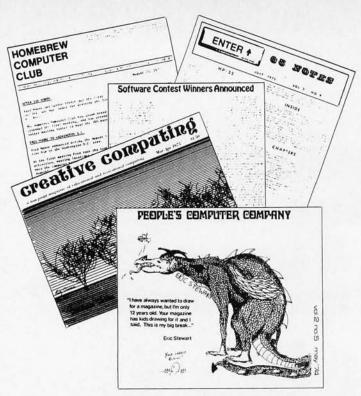

| Clubs, Newsletters            | 4 |

| Space Ace, Numbers Answer     | 7 |

| What's New                    | 8 |

| BYTE's Bits                   | 0 |

| Classified Ads                | ô |

| BYTE's Bugs8                  | 8 |

| Book Reviews                  | 2 |

| BOMB                          | ô |

| Reader's Service              | 6 |

BYTE magazine is published monthly by BYTE Publications, Inc., 70 Main St, Peterborough, New Hampshire 03458. Subscription rates are \$12 for one year worldwide. Two years, \$22. Three years, \$30. Second class postage application pending at Peterborough New Hampshire 03458 and at additional mailing offices. Phone 603-924-7217. Entire contents copyright 1976 BYTE Publications, Inc, Peterborough NH 03458. Address editorial correspondence to Editor, BYTE, 70 Main St, Peterborough NH 03458.

New BYTE phone: 603-924-7217

### **BYTE** #7

**MARCH 1976**

p. 30

p. 52

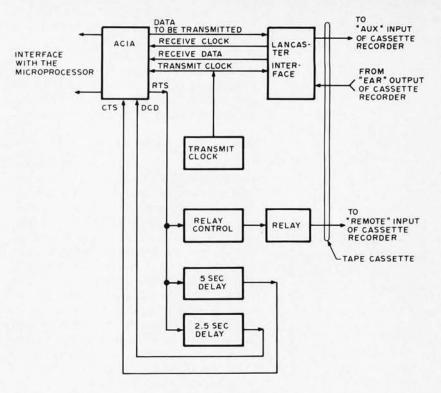

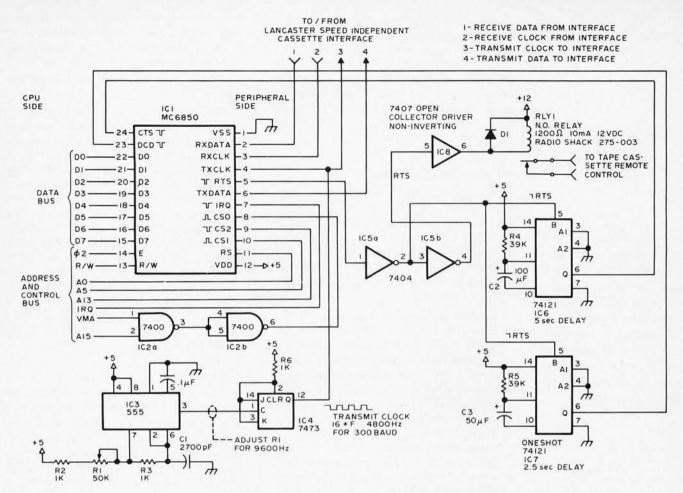

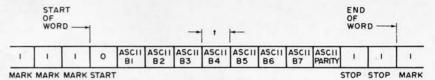

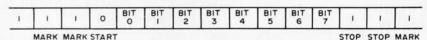

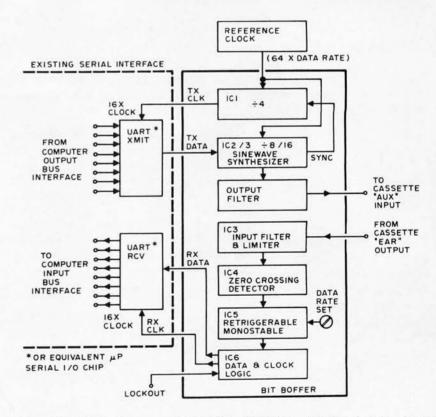

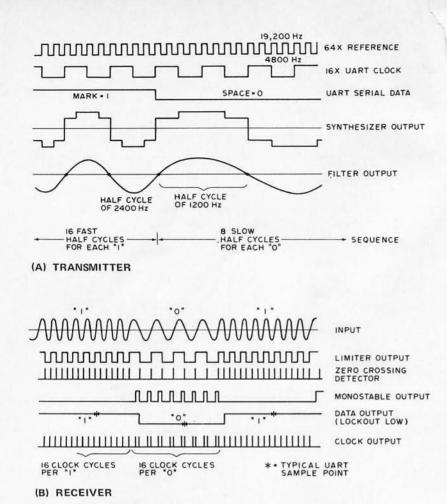

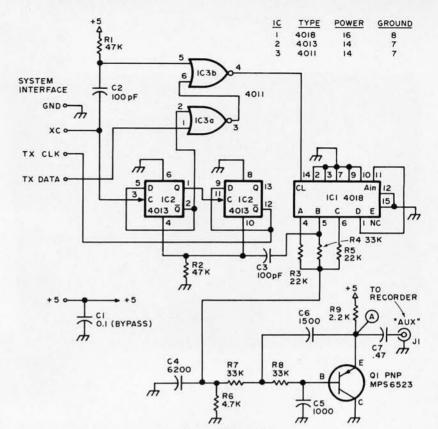

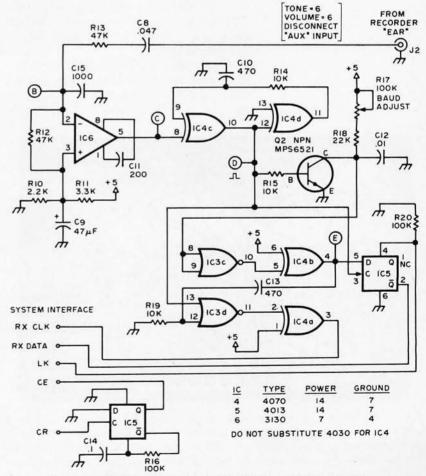

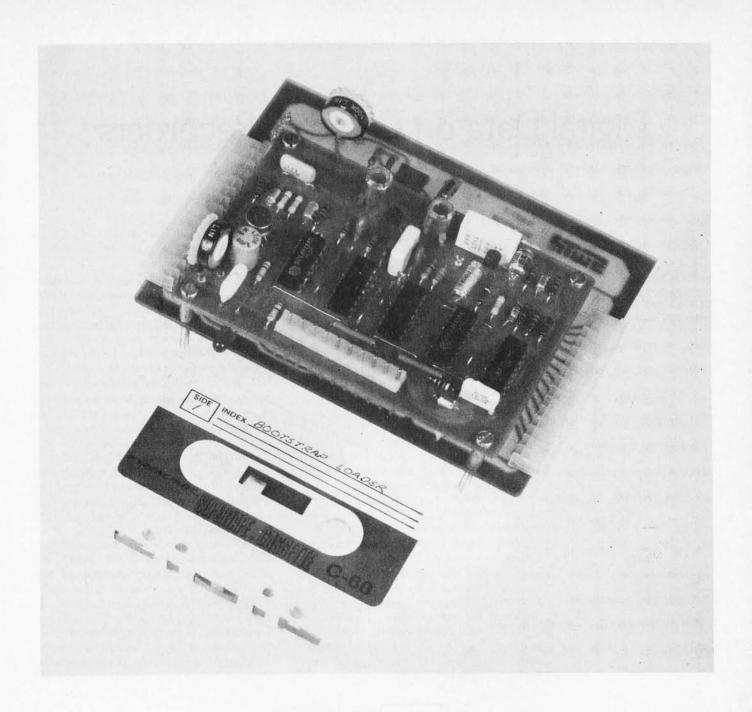

One result of the BYTE Audio Cassette Symposium last November was a provisional standard for audio recording, essentially identical to that described by Don Lancaster in issue No. 1 of BYTE last September. In this issue, Don presents an updated design and describes how to Build The Bit Boffer. Then, to show that there's more than one way to spin a tape, Harold Mauch gives some details of a second system compatible with the standard in his article Digital Data on Cassette Recorders.

In

Jack Hemenway uses Don Lancaster's Bit Boffer design to wire up The COMPLEAT Tape Cassette Interface using an ACIA attached to his 6800. But completeness requires more than hardware, so Jack provides software of six subroutines for the control and transfer of data with this interface.

## This

Creating programs can be done with a variety of tools. The best way is to use an interactive terminal with mass storage available and a good high level language. But, when you move up country or have other reasons to be away from convenient access to monster machines, at first things have to be done the hard way using a new home brew machine. This makes the techniques of Assembling Programs by Hand invaluable for your bag of tricks.

BYTE

In the previous issue, information on joysticks and slide pots was presented. In this issue, John Schulein supplies a short note on another Pot Position Digitizing Idea.

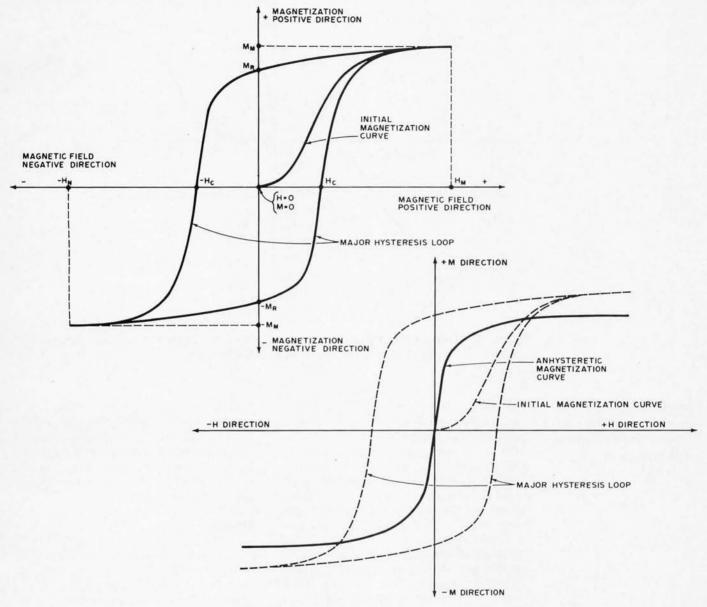

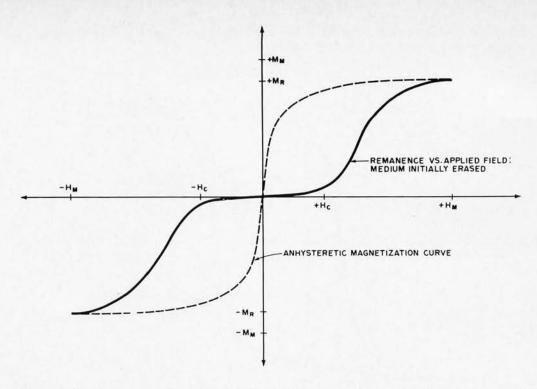

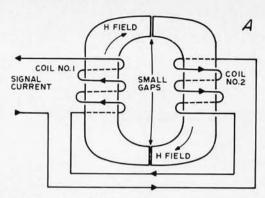

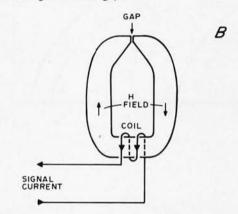

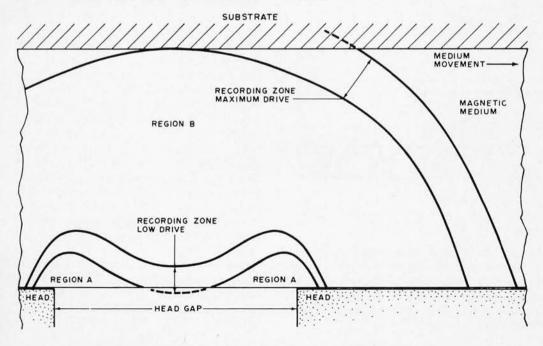

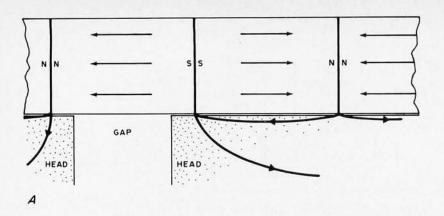

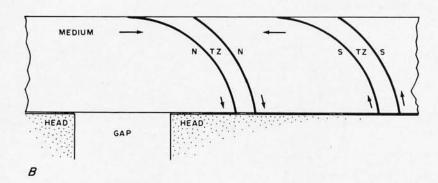

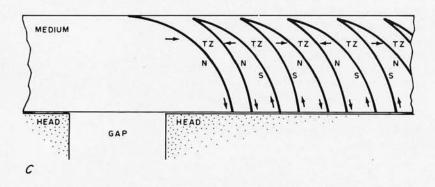

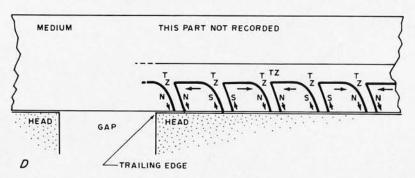

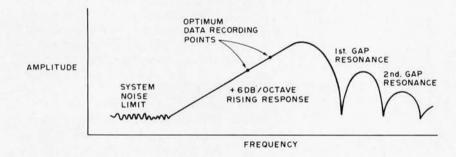

It is one thing to tell how to do something, but why it works is often a separate topic. William A Manly provides answers to a lot of the "whys" of magnetic mass storage in his article on the physics of Magnetic Recording for Computers.

One of the newer microprocessor designs is the General Instrument CP1600. In his Microprocessor Update, Bob Baker summarizes the technical information about this chip design.

Last month, Prof W Douglas Maurer described some salient points about processing algebraic expressions. In this issue, he continues the discussion with Part 2 of Processing Algebraic Expressions. This includes a simplified explanation of what it means to generate code as in a compiler.

Peek inside a video display terminal with Don Walters' quick summary of What's in a Video Display Terminal.

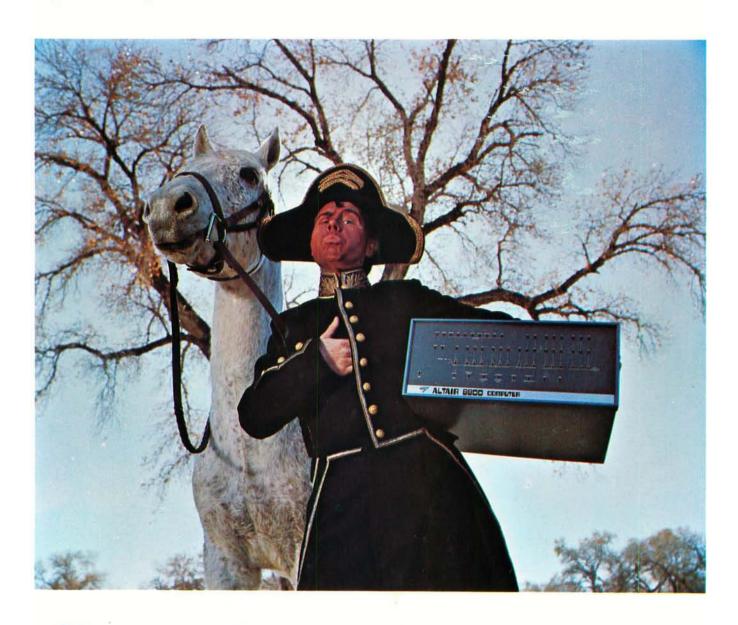

And to round out the theme of magnetic recording technology, the cover shows a typical Philips style audio cartridge.

#### Join now

Since 1947, ACM has served as *the* educational and scientific society for computing professionals—30,000 strong and growing.

#### Write today

For regular and student membership information send the attached coupon to ACM headquarters. With Special Interest Groups covering every major computing discipline and local Chapters in most metropolitan areas, ACM is probably the organization you're looking for.

| Association for Computing Machinery<br>1133 Avenue of the Americas, New York, N.Y. 10036 |

|------------------------------------------------------------------------------------------|

| I would like to consider joining ACM. Please send more information.                      |

| Name                                                                                     |

Name

Position

Address

City State Zip

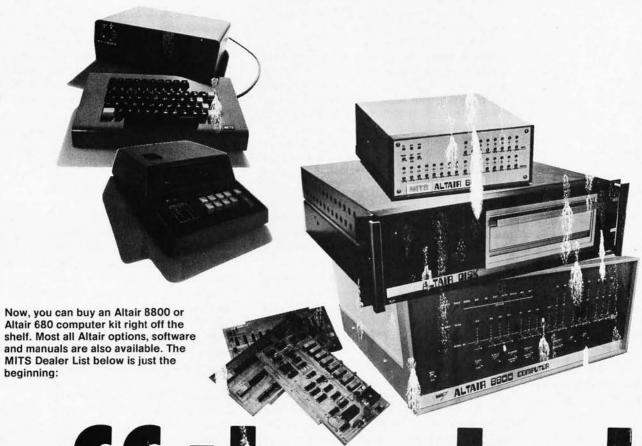

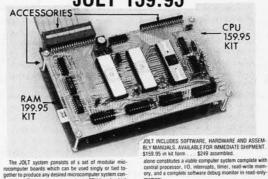

Announcing!! The world's most advanced, low cost, computer system available today!!

#### The MICRO-SPHERE 200

### SPECIAL FEATURES: \$860

- Completely Assembled and Tested (Ready to use; not a kit.)

- 4k RAM (EXPANDABLE TO 8k)

- CASSETTE LOADER

- Sphere Cassette Operating System (SCOS) supports file handling and Advanced Program Development, System, an aid for developing your programs.

- 16 Line by 21 Character Alpha Numeric Character Generator (128 by 128 B & W Dot Matrix Graphic System

- Monte Carlo Games Package

- Operators Manual

- Attractive Mar-Resistant Plastic Case

The Micro-Sphere 200 Series computer is the most ADVANCED, low-cost computer SYSTEM available today. Together with a TV and up to three cassette recorders you can have big computer performance at a rock bottom price.

The system features a 6800 type micro-computer with 4000 characters (4K Bytes) of internal Random Access Memory (RAM) Storage. The memory is easily expandable to 8000 total characters with the addition of an optional second 4K of RAM, with even more memory to be made available shortly. The 4K bytes of memory is equivalent to 6-8 pages of close typewritten material.

Access into the Micro-Sphere is achieved by the keyboard or from cassette recorders. The computer can display information on a standard TV screen (optionally supplied) or store information on a cassette recorder.

The keyboard uses highly reliable keyswitches to insure user satisfaction. It is full alpha-numeric including an integrated numeric key pad. The cassette interface uses the "Kansas City" standard which means that you can use even the least expensive cassette recorders with your system satisfactorily though we suggest that you do use high quality tapes with your system.

You may use your own TV without modification as the system display device, or you may purchase one from Sphere.

The power requirement is a single 110 volt AC outlet. The unit uses less power than an ordinary 100 watt light bulb. All fuses, jacks, switches, and interface signals are provided on an easy-access panel at the rear of the cabinet.

The Micro-Sphere is supplied with a built-in loading program from cassette, which is in one of the several standard or optional Read Only Memory (ROM) Integrated Circuits (IC).

ROM IC's are pre-programmed with specific non-eraseable information. This feature greatly reduces program loading time and inconvenience, ROM's also save valuable RAM storage. RAM's lose all stored memory whenever the computer power is turned off, while ROMs retain all programs indefinitely.

The Micro-Sphere is unique in that 16,384 different dots on your TV screen can form any number of pictures or designs which you have instructed your computer to display. These images can be changed by the computer program at a rate that appears as real-life movement, such as aircraft flight simulation, "walk-through" inspection of architectual mock-ups, time-lapse stock market graphic analysis, or even computer generated art forms, or space flight simulation where you can guide your spacecraft to the moon, planets or the universe.

You can experience the thrill of rolls, dives, loops, near-collisions and other types of aerial maneuvers to out wit the Red Baron in your Sopwith Camel and then the excitement of a victorious landing as you crash at the end of the approaching runway.

the end of the approaching runway.

This same 128 row by 128 column dot matrix can form an alpha-numeric display of up to 16 lines by 21 characters. An optional graphics input device (Mouse) digitizes hand movements when moved about on a flat surface. The "Mouse" has a window and crosshairs, so it may be used for the accurate entry of maps or other graphic data.

The mouse may also be used in the place of a joy stick for flight simulation or to enter hand movements for ping-pong or other games of skill.

| No.  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Price/Each        | Total                                                            |                                                                  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------------------------------------------------|------------------------------------------------------------------|

| 200  | MICRO-SPHERE 200 - SYSTEM PRICE INCLUDES "A" ITEMS BELOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   | \$ 860.00                                                        | \$ 860.00                                                        |

|      | 6800 type Micro-Processor unit 4K of Memory (RAM) Cassette Loading System (ROM) Sphere Cassette Operating System (SCOS) Cassette 1 time license fee@ Includes Floating Point and Trig Package Cassette copy @  "A" ITEMS Monte Carlo Games Package (Cassette) First Cassette Interface 128 by 128 B&W Dot Matrix Graphics Display Alpha-Numeric Keyboard Attractive Mar-Resistant Plastic Case Operators Manual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | \$137.50<br>12.50 | \$150.00<br>\$10.00                                              | Incl.                                                            |

|      | OPTIONS AVAILABLE THROUGH FACTORY INSTALLATION.  * To install options after purchase is \$35.00 per shipment to our plant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                   |                                                                  |                                                                  |

|      | "B" ITEMS Second 4K of memory (RAM) Character Generator (ROM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   | \$180.00<br>\$25.00                                              | \$180.00<br>\$25.00                                              |

|      | Second Cassette Interface Extended Business Basic (ROM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   | \$50.00<br>\$400.00                                              | \$50.00<br>\$400.00                                              |

|      | "C" ITEMS Includes Business Basic Manual Floating point & Trig package (ROM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   | \$130.00                                                         | \$130.00                                                         |

|      | Third Cassette Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   | \$50.00                                                          | \$50.00                                                          |

|      | OPTIONS FOR PURCHASE NOT NEEDING FACTORY INSTALLATION.  Extended Business Basic on Cassette (Requires 2nd 4K of RAM and Character Generator in ROM.) Includes Business Basic Manual, Floating Point & Trig Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   | \$100.00                                                         | \$100.00                                                         |

|      | 9" TV for use with Micro-Sphere 200 "Mouse" Graphics Input Device (Available in May 1976) Operators Manual (SCOS) Business Basic Manual Maintenance Manual Empty Cassette Tapes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2 ea.<br>3 for    | \$150.00<br>\$150.00<br>\$10.00<br>\$10.00<br>\$40.00<br>\$10.00 | \$150.00<br>\$150.00<br>\$10.00<br>\$10.00<br>\$40.00<br>\$10.00 |

| 200A | INCLUDES MICRO-SPHERE 200 PLUS ALL OF "A" ITEMS ABOVE REGULAR \$860.00 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                   | \$860.00                                                         | \$860.00                                                         |

| 200B | INCLUDES MICRO-SPHERE 200 PLUS ALL OF "A" & "B" ITEMS ABOVE REGULAR \$1215.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   | \$1215.00                                                        | \$1215.00                                                        |

| 200C | INCLUDES MICRO-SPHERE 200, PLUS ALL OF "A" & "B" & "C" ITEMS ABOVE REGULAR \$1645.00 - EVERYTHING IS IN ROM !!  ALL UNITS ARE COMPLETELY AS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | \$1645.00         | \$1645.00                                                        |                                                                  |

| SPEC | CIAL INTRODUCTORY ORDER FORM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | · ·               | NEAD T TO OBE                                                    |                                                                  |

| Item | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Quantity          | Price/Each                                                       | Total                                                            |

| 1    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                                                  |                                                                  |

| 2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                                                  |                                                                  |

| 3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                                                  |                                                                  |

| 4    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                                                                  |                                                                  |

| NAM  | AE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Item Purchas      | e Total<br>ts add 4.75% tax                                      |                                                                  |

| STRE | Production of the control of the con | dling, shipping   |                                                                  |                                                                  |

STATE

SIGNATURE

CITY:

BANK CARD NO.

PHONE NO.

STATE

SPHERE CORP. 791 South 500 West, Bountiful, Utah 84010 Tel. (801) 292-8466

ZIP

SPHERE generally offers 60-90 day delivery on its products, however, parts availability may delay delivery beyond

D. Full Warranty = 10% of A.

F. Down Payment = 25% of E.

E. Order Total

G. COD Balance

that time.

Orders may be cancelled after 120 days without penalty.

Spheres only obligation is to deliver the product. Introductory offer valid in U.S.A. only.

# Magnetic Recording Technology

## **BYTE** staff

**Editorial by Carl Helmers**

PUBLISHERS Virginia Peschke Manfred Peschke

EDITOR Carl T H

Carl T Helmers, Jr

GENERAL MANAGER

Manfred Peschke

PRODUCTION MANAGER

Judith Havey

PRODUCTION ASSISTANT

Elizabeth Alpaugh

CIRCULATION

Deborah R Luhrs

PUBLISHERS ASSISTANTS

Cheryl Hurd

Deena Zealy

ADVERTISING

Virginia Pesch ke

**TYPOGRAPHY**

Custom Marketing Resources, Inc.

Goodway Graphics

**PHOTOGRAPHY**

Ed Crabtree

Custom Marketing Resources, Inc.

DRAFTING

Bill Morello

PRINTING

Custom Marketing Resources, Inc.

The George Banta Company

**ASSOCIATES**

Hal Chamberlin

Dan Fylstra

Don Lancaster Chris Ryland No computer system is complete without mass storage of some form. Mass storage is a nice subject to talk about, but just what is it and how can it be implemented? What are the factors which affect the ability of your computer to dump and recover data in machine readable form? What are the technologies available at prices low enough to be affordable by many individuals? How is a tape interface controlled?

Much of this issue of BYTE is devoted to articles on the problem of mass storage and practical but inexpensive systems. In particular the theme is using Philips style audio recording cassettes as an inexpensive but readily available magnetic recording technology. While no claim can be made for complete coverage of every topic in the area of magnetic recording for small scale computing systems, readers should find a high concentration of personally useful information in this issue: two articles on specific hardware means of implementing the BYTE Audio Cassette Symposium's provisional standard, one article on software interfaces for control of a typical interface, and an article on the physics of magnetic recording technology. Then there are of course several short subjects on the same theme.

#### Mass Storage — What Is It?

When you purchase a machine with (for example) 4096 bytes of memory, you have the ability to store a total data content of 4096 bytes, no more. The particular number of bytes in your system is arbitrary — the fact that your random access memory is limited is always present. If this were all the memory you had, the systems and programming you could accomplish would sooner or later be limited. At any given point in time you might want to run programs requiring less than the 4096 byte limit; but it is quite likely that you'll want to have more than one such program as you build up your software repertoire.

Similarly, if all you have is main memory, what happens when the power goes off by

intention or accident? Data in the semiconductor memories used in most kits typically will not survive the loss of power.

How do you save programs against the possibility of power failure or in order to allow use of different software from time to time? The technology of off line mass storage was created to answer this question. Use of off line storage is a requirement of virtually any programmable computer system. You see it in the smallest HP-65 and SR-52 hand calculators, and in the largest of large scale systems presently in existence.

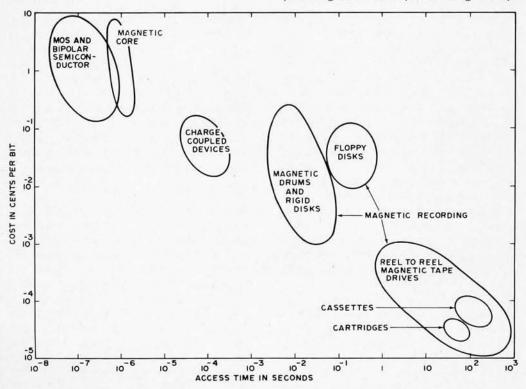

One definition of mass storage is simply, a method of storing larger amounts of data (in total) than could fit into the main memory of a given processor at one time. On large scale systems, this is usually done using disk drives and drum memories as well as other high speed high capacity random access IO devices. The typical medium priced minicomputer system uses a hard surface magnetic disk drive as its mass storage device; a removable cartridge for at least one spindle allows off line copies of data to be retained. The low priced minicomputers and high priced microcomputer systems typically use floppy disk technology at the present time. And of course the programmable calculators use miniature magnetic card IO devices to store many more programs than could possibly fit in the calculator at one time.

So what does this leave open to the low priced computer amateur's general purpose system? The answer of course is the use of audio tape technology as described by several of the articles in this issue. It is used to accomplish the mass storage function of the larger systems in an engineering tradeoff of access time against total cost. The result is a low speed but inexpensive off line storage method.

#### What Do You Use Mass Storage For?

The basic reason for off line mass storage was outlined in the previous section: making up for the limitations of a finite main

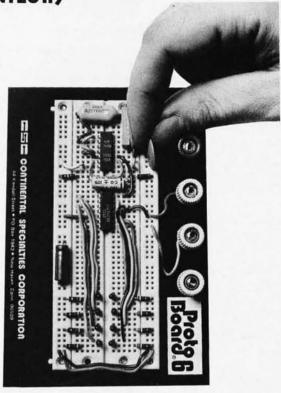

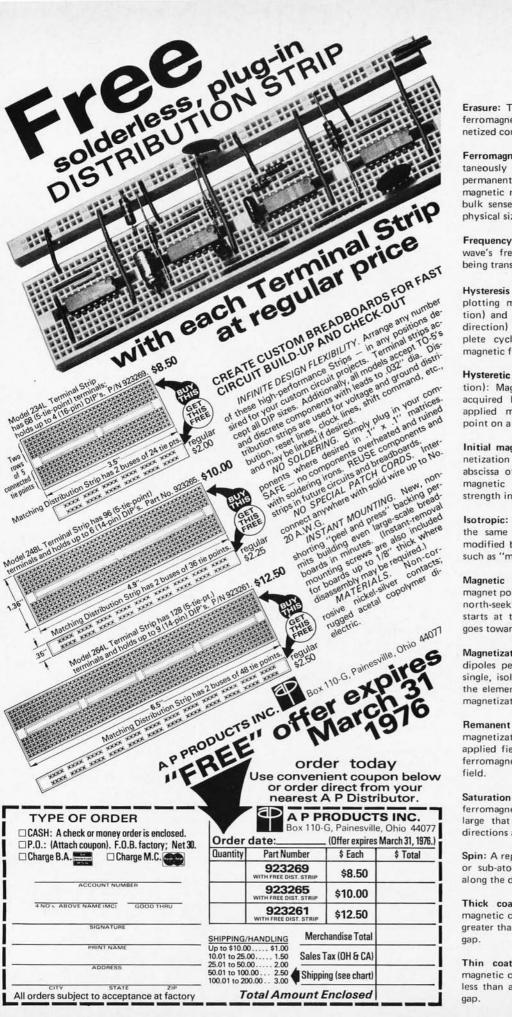

# THE SOLDERING IRON VS. THE PROTO-BOARD.

(IT'S NO CONTEST.)

#### **The Soldering Iron**

If you're still designing and testing breadboard circuits the conventional way, you're doing a lot of extra work, and getting a lot of grief in return. You've got to think as much about manual labor as you do about the circuit. Maybe even more.

Every time you add a component, there are 2 or more connections to make... over a dozen with most IC's, while watching out for overheating components and cold solder joints. And that's only half the problem.

The other half is when you want to change components or connections. Even with good desoldering equipment, you can still have a hassle on your hands. (Ever try to desolder a temperature-sensitive 14-pin DIP on a component-filled board?)

Solder. Desolder. Resolder. Desolder: Now there's a better way...

#### The Proto-Board

With the CSC Proto-Board breadboarding system, connecting components is as simple as pushing a lead into a hole. Rugged 5-point contacts insure low-resistance connections, and where jumpers are needed, components are interconnected with standard #22 AWG solid wire.

That's all there is to it.

You can choose Proto-Boards with anywhere from 630 to 3060 solderless tie-points. Proto-Boards with or without regulated power supplies. Even assemble your own, with the same solderless QT sockets and Bus Strips,\* for smaller (or larger) capacity. However you do it, you'll save time...money...aggravation...on every circuit.

For more information, see your CSC dealer or distributor...or contact us for our catalog and distributor list.

Continental Specialties Corp., 44 Kendall Street, Box 1942, New Haven, CT. 06509 • 203-624-3103 TWX: 710-465-1227 West Coast Office: Box 7809, San Francisco, CA, 94119 • 415-421-8872 TWX: 910-372-7992 Canada: Len Finkler Ltd., 25 Toro Rd., Downsview, Ontario • 416-630-9103

memory in any particular computer's implementation. The uses of the mass storage are basically similar to the uses of memory within the computer: mass storage contains program and data information. The problems of using and coordinating the use of the mass storage facility are independent of the information content of particular files. (A "file" is understood to mean a collection of related data found in the mass storage medium.)

#### Program Storage

Program storage off line is a most useful application of the mass storage facility. Programs can be stored in many ways, including memory images, relocatable programs and source programs. In this utilization the programs and subroutines become part of a software library maintained in mass storage until you need them.